| Автор |

Сообщение |

|

|

Дата: 08 Апр 2006 15:45:40 · Поправил: pav1904

#

Как-то раз я решил сделать себе PLL-синтезатор частот на широко известной русской микросхеме КФ1015ПЛ4 и мне в голову пришла мысль: а что если при вращении валкодера менять не коэффициент деления частоты ГУНа, а требуемую частоту ГУНа, причём изменять её на величину введённого в память шага изменения частоты (шага сетки). А затем уже расчитывать оба коэффициента деления (частоты кварцевого генератора и частоты ГУНа) исходя из требуемой частоты ГУНа, частоты кварцевого генератора и частоты сравнения (диапазона частот сравнения).

И сразу я сел за C++ Builder 6 и написал на нём программу для расчёта этих коэффициентов деления, при которых установится частота ГУНа с минимальным отличием от требуемой частоты. Результаты выполнения этой программы меня просто поразили: при частотах сравнения 4...5 кГц можно получить шаг сетки менее 10 Гц! Т.е. шаг сетки раз в 500 меньше частоты сравнения! Я подумал, что этот метод уже где-нибудь применяется, и начал искать в интернете что-то подобное, но нашёл только PLL-синтезаторы, использующие в качестве опорного генератора DDS-синтезатор частот, чтобы получить шаг сетки меньше частоты сравнения. И ещё нашёл схемы фракциональных PLL-синтезаторов, использующих дробный коэффициент деления частоты ГУНа, но этим схемам присущи многие недостатки, в частности с увеличенным временем установления частоты. Незнаю, был-ли описан где-нибудь подобный метод, о котором я додумался, но вот результаты:

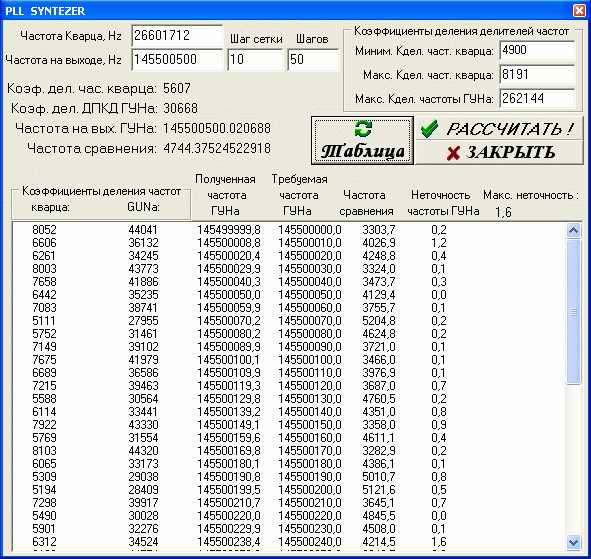

Я взял кварц для опорного генератора от известной приставки DENDY. Его частота: 26601712 Гц.

Синтезатор построен на микросхеме КФ1015ПЛ4 и даёт частоты (на скрин-шоте моей программы) в любительском диапазоне 145 МГц, с шагом сетки 10 Гц.

В таблице представлены: слева - расчитанные программой коэффициенты деления частоты кварца и частоты ГУНа, правее - полученная частота ГУНа, и требуемая частота ГУНа, ещё правее - ошибка в установлении частоты (на сколько отличается требуемая частота от получившейся с расчитанными коэффициентами деления)

Как видите ошибка установления частоты значительно меньше шага сетки, значит при необходимости можно шаг сетки сделать ещё меньше - например 5 Гц.

Минимальный и максимальный коэффициент деления частоты кварца задаётся с целью ограничить диапазон частот сравнения чтобы использовать один и тот-же Low-Pass фильтр во всём диапазоне частот сравнения.

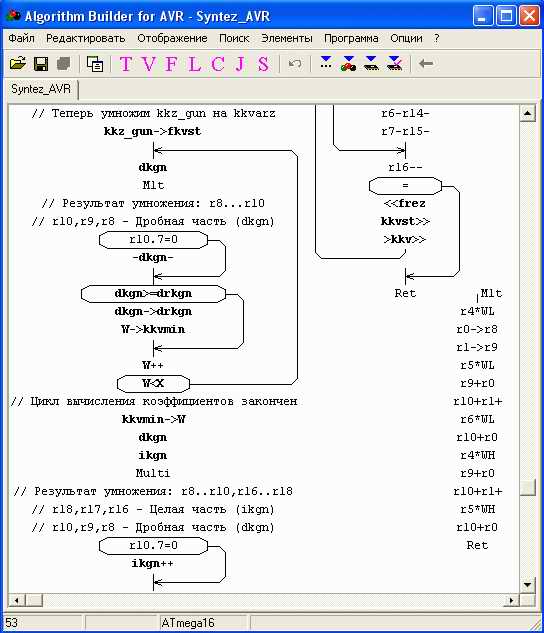

Далее я написал эту программу для микроконтроллера фирмы Atmel ATMega16 в Algorithm Builderе, и уже в готовом синтезаторе частоты при вращении валкодера этот контроллер расчитывает коэффициенты деления частот кварцевого генератора и ГУНа. Маленький фрагмент этой программы Вы можете видеть на следующем скрин-шоте:

Здесь как раз виден цикл, в котором и расчитываются коэффициенты деления частот при требуемой частоте ГУНа. |

|

|

Дата: 08 Апр 2006 16:17:50

#

pav1904

В любом случае мои поздравления, даже если вы и не первый, это ваша личная победа... теперь о грустном... практически реализуйте в работающую конструкцию все изложенное. ;) Не однократно был уже и "миллионером" и "гением" теоретически конечено, практическая реализация обычно вскрывает не видимые в творческом порыве мелочи, о которые и разбивается вся прелесть идей.

|

Реклама

Google

|

|

|

|

Дата: 08 Апр 2006 19:28:28

#

pav1904

очень кстати интересно. По идее единственной проблемой могут стать поражёнки, которые будут в соответствии с каким то законом скакать попятам за частотой гуна. Хотя может быть этого и не будет.

|

|

|

Дата: 08 Апр 2006 20:43:57

#

PLL с нечеткой частотой сравнения, нету для него наверное ниши.

Если метрологи и не зарубят, то DDS придут и сгонят с насиженного было места.

|

|

|

Дата: 08 Апр 2006 20:51:09

#

Проблем с таким подходом достаточно, как только pav1904 попробует все это воплотить в железе, он на них наткнется, может быть ему и удастся их решить, а может в процессе решения он выйдет на что нибудь другое, этим надо просто заняться, по настоящему в плотную.

|

|

|

Дата: 08 Апр 2006 20:57:43

#

фильтровать сложно будет сигнал с выхода ЧФД. Соответственно - шуметь эта балалайка будет здорово.

|

|

|

Дата: 08 Апр 2006 22:14:14

#

Altair

В яблочко, нужно было не только ошибку частоты ГУНа считать, но и разброс частоты сравнения, на которой будет работать ФАПЧ, и тут возникают большие неприятности. ;)

|

|

|

Дата: 08 Апр 2006 22:32:12 · Поправил: pav1904

#

Mirror

Ну так я же там написал, что с целью ограничения диапазона частот сравнения я в программе ограничил минимальный и максимальный коэффициент деления частоты кварцевого генератора! Читайте внимательнее же! А при изменении частоты сравнения в 1,5 раза нет необходимости менять Low-Pass фильтр. Об этом там написано!

|

|

|

Дата: 08 Апр 2006 22:40:35

#

Mirror

Да, а как-же по-Вашему ведущие фирмы изготовители КВ SSB-радиостанций делают синтезаторы частоты DDS+PLL где DDS-в качестве опорного генератора, и его частота является частотой сравнения. И она изменяется! И у них никаких неприятностей!

|

|

|

Дата: 08 Апр 2006 23:04:20

#

Мои поздравления!

При конструировании синтезаторов с ФАПЧ большое внимание уделяют фильтрации и как следствие оставляют частоту сравнения неизменной , изменяя коэффициент деления ГУНа частота сравнения остается постоянной. Вот тут все это подробно описано П. Хоровиц, У. Хилл. ИСКУССТВО СХЕМОТЕХНИКИ.

А в Вашем варианте шуметь это все будет.

С уважением.

|

|

|

Дата: 08 Апр 2006 23:18:05

#

pav1904

Тут прозвучала правильная мысль, надо начать это делать, фирмы используешие DDS+PLL решают массу проблем, и не всегда успешно, на любой аргумент вы будете выдвигать контраргумент, а это не продуктивно, зачем спорить, когда легко все проверяется, при вашем желании конечно. Не начав делать вы вообще ни поймете в чем трудности, потому что их сейчас просто не видно.

|

|

|

Дата: 08 Апр 2006 23:47:05

#

Mirror

надо начать это делать

зачем спорить, когда легко все проверяется

Вы правы! Действительно легко всё проверяется! Желание делать конечно у меня есть.

С уважением к Вам!

|

|

|

Дата: 08 Апр 2006 23:51:18

#

Спасибо большое вам всем за поздравления! Приятно когда меня поздравляют! =)))

Эта идея будет проверена в железе!

|

|

|

Дата: 09 Апр 2006 00:04:17

#

pav1904

на которой будет работать ФАПЧ, и тут возникают большие неприятности. ;)

А вот это вы узнаете после сборки. А вообще мысль интересная и имеет право на жизнь!!

|

|

|

Дата: 09 Апр 2006 22:35:27

#

009

Спасибо, что дали право на жизнь моей мысли! =)

|

|

|

Дата: 09 Апр 2006 23:21:05 · Поправил: GenaSPB

#

Все-таки, главной, основной, самой большой, непреодлимой (в случае жестко заданных требований) проблемой может оказаться именно переменная частота сравнения синтезатора. Практически двухкратное изменение ее (причем, в любой точке диапазона) - и меняется - чувствительность ФАПЧ к изменениям стабилизируемого генератора. Ну про подавление частоты сравнения я уж молчу... Для обеспечения захвата в петле и прогнозируемого качества сигнала ФНЧ должна быть расчитана... и расчитывается это на вполне конкретныэ полосу пропускания. Правда, это все можно "вылечить", например, тремя режимами работы ФНЧ за фазовым детектором... или, изменяя ток charge pump, если такая регулировка есть в указанной микросхеме... Так что, DDS для особо мелких сеток в бюджетных (и не очень) системах это сейчас вполне себе решение.

Расчеты в случае применения DDS будут вот такими:

http://forum.cqham.ru/viewtopic.php?p=63053#63053

И демонстрашка по расчетам:

http://www.cqham.ru/dds_prog.htm |

|

|

Дата: 10 Апр 2006 10:33:05

#

Все-таки, главной, основной, самой большой, непреодлимой (в случае жестко заданных требований) проблемой может оказаться именно переменная частота сравнения синтезатора.

Добрый день ! В самом деле, переменная частота сравнения не есть гуд. Когда я делал свой синтез, составленный из DDS и умножителя на PLL, то как раз и гонял коэффициенты деления в канале опорной частоты и ГУНа с целью того, чтоб результирующая частота сравнения на ЧФД микросхемы PLL менялась в небольших пределах, при том, что частота с выходя DDS (и блока ГУНов) менялась в 2 раза.

Что касается переходу к PLL и реализации мелкого шага. Сейчас это кстати актуально. Цены на DDS-микросхемы все растут и растут, да и сроки поставки уже не сравнить с тем что было 2 года назад.

Самый простой вариант - уйти от однопетлевой схемы. Всего на трех ИС КФ1015ПЛ4 можно сделать синтезатор перекрывающий 62-110МГц с шагом 1 или 5 Гц.

|

|

|

Дата: 10 Апр 2006 11:05:30

#

CO2040

Цены на DDS-микросхемы все растут и растут, да и сроки поставки уже не сравнить с тем что было 2 года назад.

Серьезно?

И чем это объясняется?

|

|

|

Дата: 10 Апр 2006 12:07:48

#

И чем это объясняется?

Трудно объяснить. Остаются только догадки из разряда конспиралогии. Но факт есть.

|

|

|

Дата: 10 Апр 2006 21:08:05

#

Цены на DDS с 1995г. заметно не изменились, всегда были серьезные DDS и DDS попроще.

А до этого были Gec Plessey, которые везлись через Германию ночью.

А до Gec Plessey был DDS на 500ИП161, к сожалению он утрачен, но осталась печатка, история может надеяться на его возвращение (12-500ИП161, 20-500ИЕ137, 8-500РУ415, 10-разных, -5,2V 30A персональный источник и 8кГ радиатор)

Сейчас беру AD9954, эту прозу жизни по 24$, ждать 4-6 недель а Аргуссофте.

А вообще сторонник раздельных DDS и DACа.

|

|

|

Дата: 10 Апр 2006 22:21:47

#

CO2040

барахлион

А до каких частот (приблизительно) работают сейчас широкодоступные DDS?(такой чайницкий вопрос)

|

|

|

Дата: 11 Апр 2006 00:31:00

#

AD9954 - 400МГц такт, теоретически до 200 значит

|

|

|

Дата: 11 Апр 2006 00:54:48

#

Salesperson

Как показает практика применения DDS, лучше не подниматься выше 1/3 от тактовой частоты, хотя есть и другие мнения. Современная технология позволяет работать с тактовой частотой выше 3 ггц, вероятно AD скоро преодолеет этот рубеж.

Если обратится к прогнозам, то и до 10 ггц могут добраться в обозримом будующем. Что касается достпных DDS смотри тут http://www.analog.com/ , AD9858 имеет Master fclk 1000mHz. |

|

|

Дата: 11 Апр 2006 01:27:52

#

А чё цены на DDS ? Взять любой контроллер со встроенным ЦАП и ОЗУ рублей за 150, и написать к нему программку - вот вам и DDS готовый, работающий до частот где-то 100 кГц. А больше и не надо! Дальше поставить PLL, которая будет умножать эту частоту во сколько нужно раз.

|

|

|

Дата: 11 Апр 2006 22:37:43

#

у DDS есть хорошая особенность - отсутствие разрыва фазы при сканировании, для меня это важно

да и паразиты начинаются после 1/2 от CLK .

Причем - хорошие паразиты !

Ставя набор полосовых фильтров получаем генератор от Fclk/2`N до 6Fclk.

|

|

|

Дата: 12 Апр 2006 11:13:34

#

AD9954 - 400МГц такт, теоретически до 200 значит

До 160 МГц !!!! Во всех даташитах на 995x серию пишется.

Как показает практика применения DDS, лучше не подниматься выше 1/3 от тактовой частоты, хотя есть и другие мнения.

Реально - не более 1/20 Fclk (практически для всех DDS от AD), это и в даташитах видеть опять-таки можно и собственными измерениями к этому пришел. Выше - уже существенно ухудшается соотношение сигнал/шум. А это вещь принципиальная, особенно если DDS планируется использовать как перестраиваемую "опору" для PLL.

|

|

|

Дата: 12 Апр 2006 12:54:43

#

CO2040

http://www.analog.com/UploadedFiles/Data_Sheets/31685232434714AD9954_0.pdf

есть еще Qualcomm, Peregreen и Stanford - уних за 5ГГц Fclk перевалила

|

|

|

Дата: 12 Апр 2006 15:50:12 · Поправил: GenaSPB

#

[Задумчиво...] А какими соотношениями описывается уровень тактового сигнала по отношению с синтезированному? Интересует для системы - тактовая 10 МГц, несущая - 700 кГц, выделяем image 10.7 МГц? И главное, все холодное!

Естественно, уровень на выходе синтезатора. Судя по картинкам в описании, уровни в порядке убывания распределяются так: fundamental, image(s), Fclk. Интересует, на сколько будет подавлена Fclk. Знаю, что зависит от каждого конкретного соотношения... но порядок хоть какой? -6 дБ, -20 дБ?

[img][/img]

|

|

|

Дата: 12 Апр 2006 17:17:06

#

GenaSPB надо давить внешним ФНЧ, 3-звенного хватает

а до Fclk/2 уровень паразитов определяется разрядностью ЦАП L=nx6dB

Fвых=Fclk/N

|

|

|

Дата: 12 Апр 2006 17:27:06

#

Я, вообще-то, говорил об самом Fclk... и об image, который выше Fclk...

|

Реклама

Google |

|